时钟

晶振尽可能放置于IC附近,建议不超过4 mm,这将最大限度地减少输入引脚上的额外容性负载,并降低晶振与其他信号串扰和干扰的可能性。另外,请确保在晶振下方或晶振走线旁边无其他信号线。32 MHz晶振走线尽可能包地处理,如晶振下方有完整地平面并没有其他干扰信号的情况下,可在晶振焊盘正下方可做开窗处理,减小焊盘寄生电容。

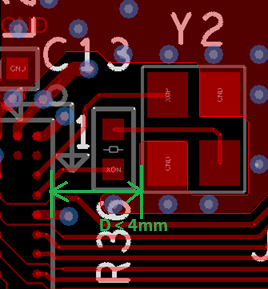

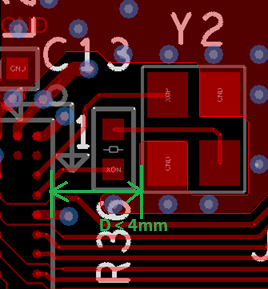

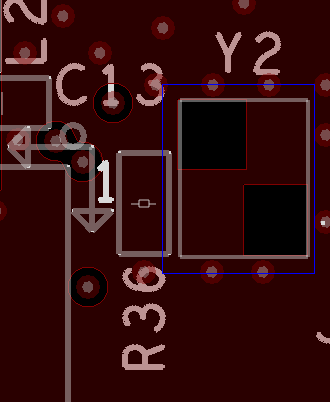

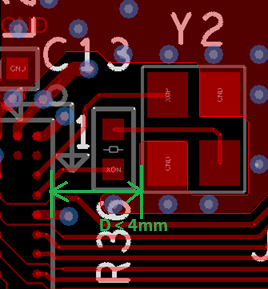

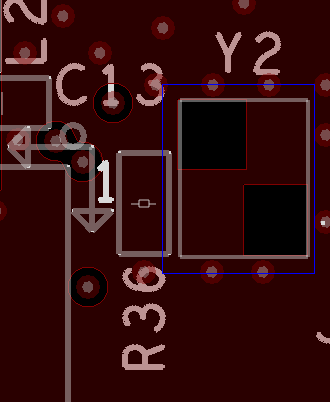

图 16 GR5515RGBD PCB参考时钟布局

打开微信,使用“扫一扫”即可关注。