QFN56 PCB四层板参考设计

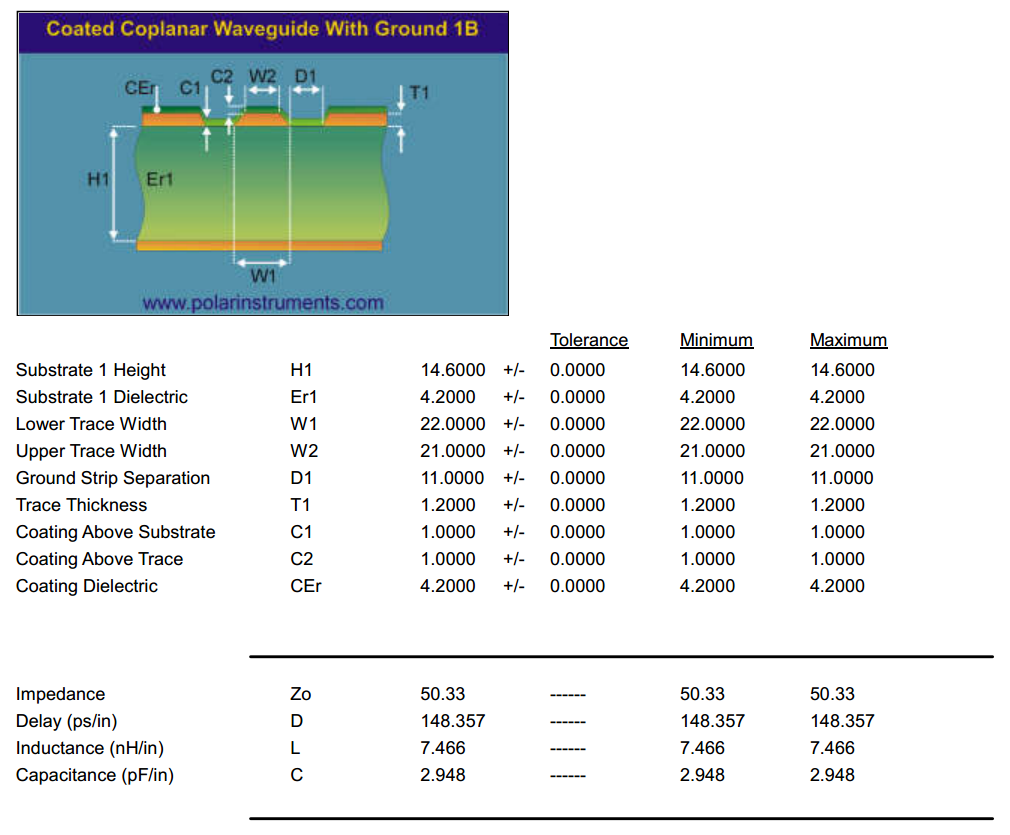

本例的PCB Layout参考设计将所有的GPIO信号从芯片中引出。采用四层板的设计,板厚0.6 mm,过孔全为通孔,射频线走线宽度为22 mil,与匹配器件的焊盘同宽。由于PCB板较薄,为保证射频传输线的50 Ω阻抗控制,第二层进行了挖空,使用第三层(使用0.6 mm板厚50 Ω阻抗控制参考叠层设计,如图 34所示)作为参考地平面。

详细PCB Layout参考设计如下。

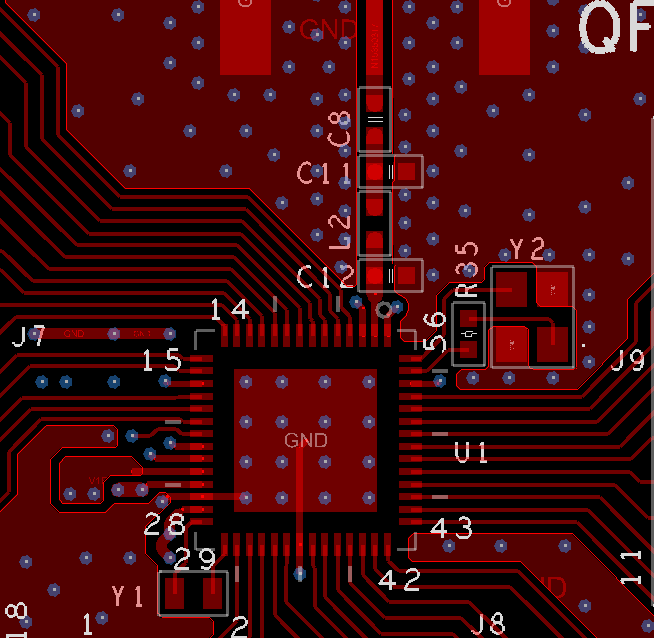

- TOP层

用于元器件布局和RF等关键信号走线。

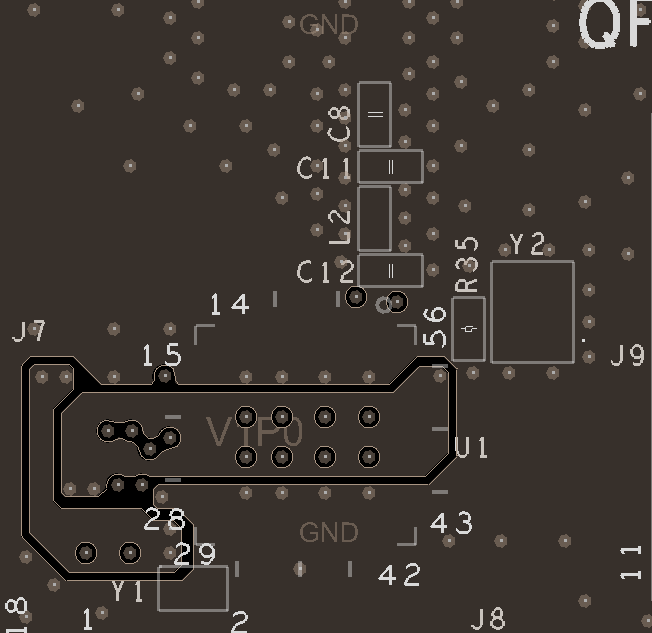

图 35 TOP层设计 - L2层

用于信号返回接地层,本例按照板厚0.6 mm阻抗控制叠层设计做了50 Ω射频传输线隔层参考的地平面挖空处理,以及32 MHz晶振焊盘下方的地平面挖空处理。

图 36 L2层设计 - L3层

用于电源和少量走线。本例中该层作为射频线的参考地层,注意保证射频传输线走线下方的接地平面完整。

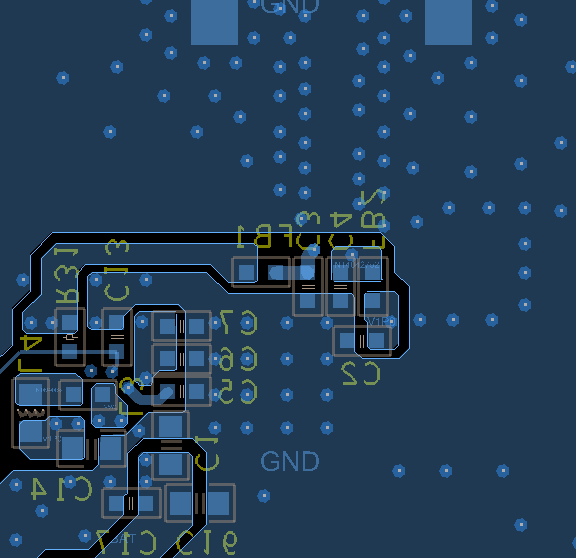

图 37 L3层设计 - BOTTOM层

用于滤波器件的布局和信号走线,滤波器件尽可能靠近对应的芯片管脚。

图 38 BOTTOM层设计