电源

电源框图简介

GR551x是通过引脚VBATL外接电源供电,供电范围为1.7 V ~ 3.8 V。

需要采用单独外部稳压器LDO供电,建议选择低压差、静态电流Iq小的LDO(小于产品待机下的规格要求),LDO输出电流需大于100 mA,LDO输出电压3.3 V(典型值),负载调整率(10% ~ 120% Iout)需小于10 mV。

LDO的最大输入电平若大于5.5 V,为防止在调试时热上电过冲,需要在LDO输入端串接0.39 Ω ~ 1 Ω小电阻。

GR551x的电源管理子系统的功能框图,如图 7所示。

电源管理子系统主要负责为芯片中的各模块提供电源电压。

- I/O LDO稳压器为片上Flash(GR5515I0ND和GR5515I0NDA除外)以及芯片的I/O引脚提供电源电压。关于I/O LDO的详细介绍,请参考I/O LDO。

- 在Active模式下,DC-DC开关电源为收发器供电,Digital LDO稳压器为数字模块供电。

- 当MCU子系统和BLE子系统都被关闭时,将由Lower Power LDO为芯片的AON(Always On)部分供电。它还为内存的数据备份区域提供低电压电源,以便从睡眠模式唤醒后恢复保存在内存中的数据内容。

- 数据备份区域和数字模块的电源电压将通过矩阵开关分配给芯片的所有电源域。

电源电路原理图

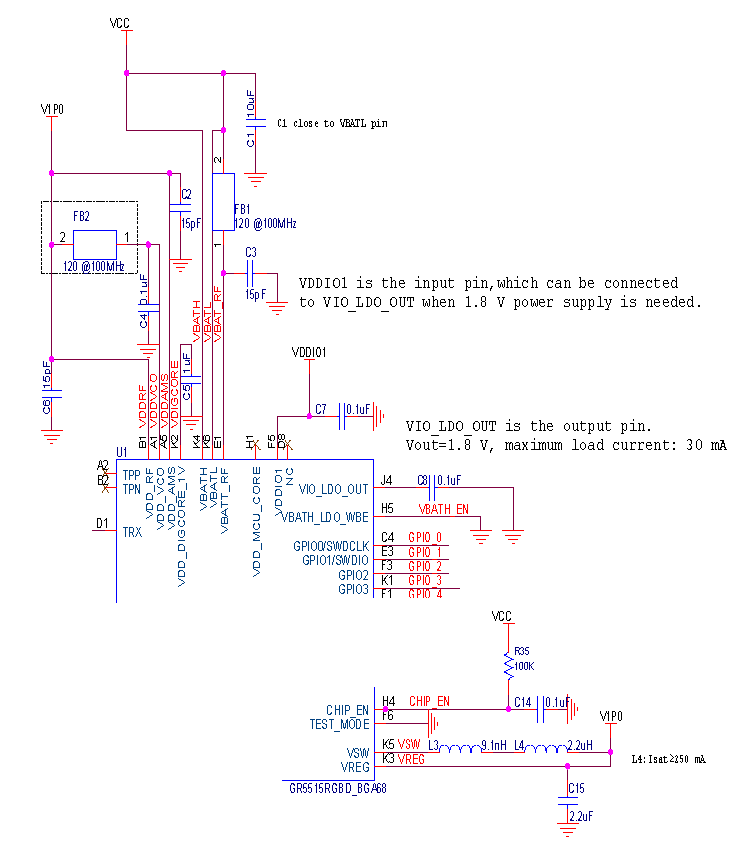

GR551x SoC内部包含所有电源管理模块,以保证系统的正常和安全运行。以BGA68封装为例,电源模块的电路设计参考如图 8所示。

各引脚的功能以及连接描述如下:

- VDD_VCO/RF:内部射频部分的供电引脚。连接至DCDC开关电源的输出电压网络V1P0,连接一个0.1 µF滤波电容。

- VDD_AMS:内部射频部分的供电引脚。连接至DC-DC开关电源的输出电压网络V1P0,连接一个15 pF滤波电容)。

- VDD_DIGCORE_1V:Digital LDO的输出引脚,为数字内核逻辑供电。连接一个1 µF滤波电容。

- VBATL:芯片电源输入,电压范围:1.7 V ~ 3.8 V。连接一个10 µF滤波电容。

- VBATH:连接至VBATL引脚,仅BGA68封装有这个PIN脚。

- VBATH_LDO_WBE:默认接地。

- VDD_MCU_CORE:数字内核的电源,默认不连接,仅BGA68封装有这个PIN脚。

- VBATT_RF:连接至VBATL引脚。

- VIO_LDO_OUT:片上VDDIO LDO电源的输出引脚(在芯片内部默认和VDDIO0连接),主要为内置Flash供电,也可为VDDIO引脚或外部传感器供电,可提供高达30 mA的负载电流。连接一个0.1 µF去耦电容。

说明:GR5515I0ND和GR5515I0NDA外置Flash支持高电压(VDDIO0为3.3 V或VBATL)供电,GR5515IENDU和GR5513BENDU内置Flash支持宽压1.65 V ~ 3.6 V供电。当用户需要使用高压模式时,其设置如下:

- 系统启动时会根据eFuse配置自动关闭I/O LDO。

- VIO_LDO_OUT只作为VDDIO0数字电压域输入,将其连接到3.3 V或VBATL。

- VSW:DC-DC开关电源的输出引脚。连接两个电感(串联):一个为9.1 nH电感(用于减少开关噪声引起的射频干扰),另一个为2.2 μH功率电感,以及一个2.2 µF电容,组成完整的DC-DC电路,输出V1P0电压给芯片供电,需通过外部电路连接到VDD_RF、VDD_AMS、VDD_VCO引脚上。

- VREG:DC-DC开关电源输出电压的反馈引脚,连接至V1P0电压网络。

- VDDIO1:IO1电压域供电引脚,可由VIO_LDO_OUT或者外部稳压器供电,连接一个0.1 µF滤波电容。

以上使用的电容,磁珠以及电感的元器件选型,可参考表 7和表 8。

| 符号 | 描述 | 值 | 封装类型 | 推荐器件(制造商、型号) |

|---|---|---|---|---|

| C15 | CAP CER X5R 10% 6.3 V | 2.2 µF | 0603 | Murata GRM188R61C225KE15D |

| C4,C7,C8,C14 | CAP CER X7R 10% 10 V | 0.1 µF | 0402 | Murata GRM155R71A104KA01D |

| C5 | CAP CER X5R 10% 6.3 V | 1 µF | 0402 | Samsung CL05A105KO5NNNC |

| C1 | CAP CER X5R 20% 10 V | 10 µF | 0603 | Murata GRM188R61A106ME69 |

| C2,C3,C6 | CAP CER NPO ±5% 50 V | 15 pF | 0603 | AVX 04025A150JAT2A |

| FB1,FB2 | Ferrite Bead, 120 ohm @100 MHz, 400 mA, 500 mOhm, 0603 | 120@100 MHz | 0603 | Murata BLM18AG121SN1 |

| 符号 | 值 | DC电阻(最大值) | 饱和电流 | 长x宽x高(mm) | 推荐器件(制造商、型号) |

|---|---|---|---|---|---|

| L3 | 9.1 nH | 0.32 Ω | 300 mA | 1.0 x 0.5 x 0.5 | Murata LQG15HS9N1J02D |

| 符号 | 值 | DC电阻(typ值) | 饱和电流 | 长x宽x高(mm) | 推荐器件(制造商、型号) |

|---|---|---|---|---|---|

| L4 | 2.2 µH ±20% | 0.3 Ω | 250 mA | 1.6 x 0.8 x 0.8 | Sunlord MPH160809S2R2 |

| 0.2 Ω | 250 mA | 1.6 x 0.8 x 0.8 | Murata LQM18PN2R2MGH |

||

| 0.38 Ω | 300 mA | 1.6 x 0.8 x 0.8 | Murata LQM18PN2R2MFH |

2.2 µH的功率电感用于PSM(Pulse Skip Mode)模式的DC-DC buck电路中,且对整个DC-DC电路至关重要。它的饱和电流需大于250 mA,同时它的直流电阻会影响功耗,因此饱和电流大、直流电阻小的功率电感器件有利于系统的安全运行和性能提升。

I/O LDO

GR551x的I/O LDO默认输出1.8 V的额定电压,为片上Flash(GR5515I0ND和GR5515I0NDA除外)和芯片的I/O引脚(VDDIO0引脚)供电。此外,它还可为传感器等外围器件供电,最高负载电流为30 mA。

I/O LDO的电源输出引脚为VIO_LDO_OUT,该引脚需连接一个0.1 µF去耦电容。

GR551x的IO电压域包括三个:VDDIO0、VDDIO1两个数字电压域以及一个MSIO数字混合电压域,对应的参考电平分别为VDDIO0、VDDIO1、VBATL。其中VDDIO0在芯片内部和VIO_LDO_OUT相连,未单独连接到封装引脚上。VIO_LDO_OUT与IO电压域关系如下图:

I/O LDO的漏电电流约0.7 µA。

VIO_LDO_OUT在内部和Flash的电源相连,因为Flash工作电压是1.8 V,所以VIO_LDO_OUT默认电压为1.8 V(GR5515I0ND、GR5515I0NDA、GR5513BENDU和GR5515IENDU除外),当VDDIO1和VIO_LDO_OUT外部相连后,芯片整个IO域为1.8 V(MSIO除外)。如需要改变VDDIO1对应的IO电压域,可使用外部电源为VDDIO1引脚供电,供电范围为1.8 V ~ 3.3 V,则VDDIO1对应的GPIOs的电平范围跟随外部输入电压而改变,当外部输入VDDIO1电压时,要注意不能超过电源VBATL的输入电压。

- 系统启动时会根据eFuse配置自动关闭I/O LDO。

- VIO_LDO_OUT只作为VDDIO0数字电压域输入,将其连接到3.3 V或VBATL。

VDDIO1电压域对应的I/O引脚为GPIO0 ~ GPIO15,在芯片内部和VIO_LDO_OUT相连的VDDIO0电压域对应的I/O脚为GPIO16 ~ 31和AON_GPIO0 ~ AON_GPIO7。