电源

电源是保证芯片可靠运行的基本要素,电源处理不当会带来ESD性能差、辐射超标等整机系统问题。所以在PCB设计时需要优先处理好关键电源的布局和走线。其中DC-DC电源和RF输入电源尤为重要,需遵循以下设计要求。

DC-DC开关电源

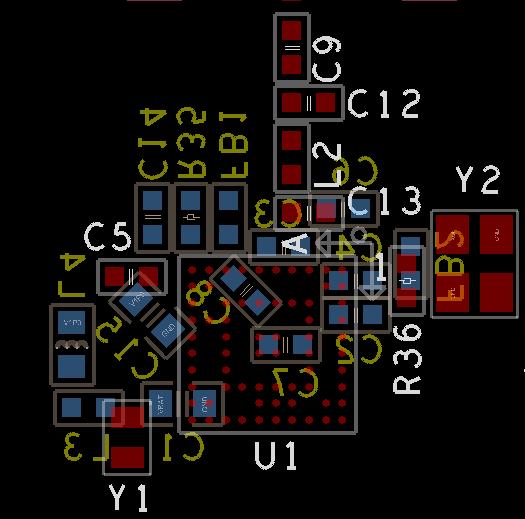

以GR5515RGBD为例,芯片内置DC-DC开关电源,DC-DC的PCB layout需满足以下设计要求:

- DC-DC电源输出外围器件L3(电感9.1 nH)、L4(电感2.2 µH)和C15(2.2 µF)应尽可能靠近芯片VSW和VREG引脚,建议距离不超过3 mm。

- DC-DC电源输出的VSW在没有经过电感之前干扰比较强,因此需要和其它网络保持至少0.2 mm的间距要求。主要会影响V1P0和DIGCORE电源。

- 电感L3(9.1 nH)和L4(2.2 µH)最好垂直放置,避免电感耦合。电容C15(2.2 µF)应放置在电感L4之后,且VREG反馈调节电源应在电容后取电。

- 电容的接地脚应尽可能靠近芯片VSS_BUCK接地脚,电容的地脚器件焊盘就近打地过孔,建议和芯片的主地引脚用地平面连接,使电源路径回路最短 。

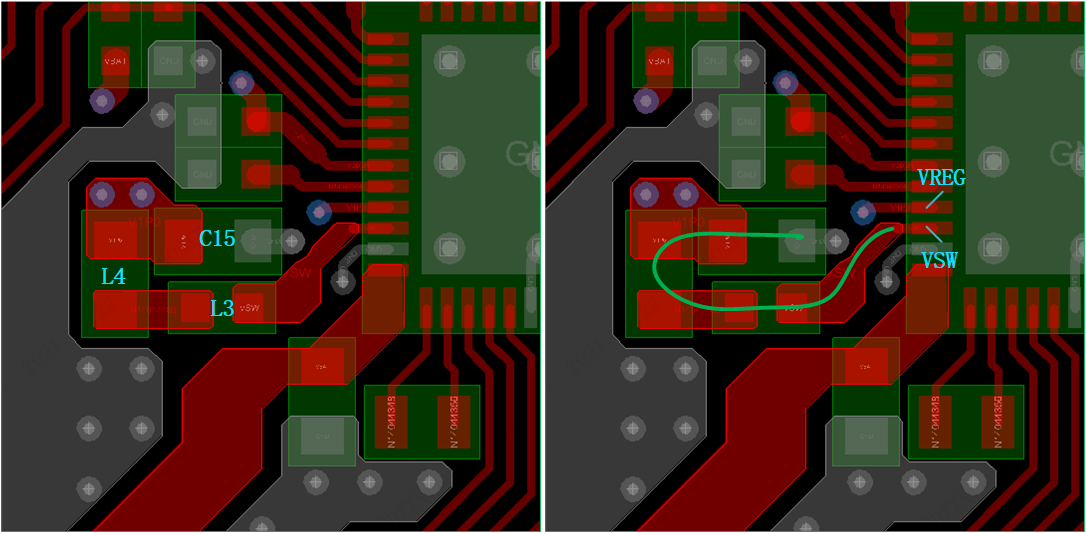

说明:

图 13中绿色线为输出电源路径。

RF输入电源

RF输入电源端是一个非常重要的设计点,如处理不好会引起诸多辐射超标的问题,RF输入电源端PCB layout设计需满足如下要求:

- RF输入电源VDD_RF、VDD_VCO、VDD_AMS的去耦电容都应尽可能靠近各芯片的引脚处,最好控制在1 mm左右,不要超过3 mm。尽量保证与芯片在同一面 ,且路径需要先经过电容再到芯片电源引脚(即如果换层连接,过孔需要打在去耦电容附近)。

- 电源走线应尽量短,宽度尽量粗,至少保证线宽0.2 mm以上,并和其它网络能够保持大于等于0.2 mm的间距 。

参考图 15,将C1(10 µF电容)放置在VBATL引脚旁,C4、C7、C8(0.1 µF电容)分别靠近VDD_VCO、VDDIO1和VIO_LDO_OUT引脚,C2、C3、C6(15 pF电容)分别靠近VDD_AMS、VBATT_RF和VDD_RF引脚,C5(1 µF电容)靠近VDD_DIGCORE_1V引脚。